В работе представлена новая архитектура строго обратимого преобразования двоичных массивов, основанная на двухслойной структуре с динамически адаптируемыми порогами активации и управляемыми криптографическими ключами. Каждый элемент массива функционирует аналогично нейрону с пороговой активацией, однако, в отличие от классических нейронных сетей, веса связей не формируются при обучении, а задаются фиксированно или модулируются ключом, а пороги динамически изменяются для обеспечения строгой обратимости системы. Предложенное преобразование реализует блочное шифрование, где размер блока равен размеру массива N×N, а процесс шифрования/дешифрования состоит из фиксированного числа шагов, структура которых допускает полную параллельную реализацию. Архитектура идеально подходит для аппаратной реализации на FPGA и нейроморфных чипах (Intel Loihi, IBM TrueNorth), где локальные связи и параллельная обработка позволяют достичь высокой скорости и энергоэффективности. Система экспериментально верифицирована на массивах 7×7 и 77×77, подтверждена строгая обратимость и отсутствие коллизий траекторий. Концептуальное доказательство обратимости имеется у автора; формализация предлагается как направление для дальнейших исследований.

Введение

Современные криптографические системы, такие как AES или ChaCha20, основаны на сложных раундовых преобразованиях, S-блоках и таблицах подстановок, что делает их вычислительно затратными при реализации на аппаратном уровне. В данной работе предлагается альтернативный подход — архитектура, вдохновлённая принципами работы нейронных сетей, но лишенная необходимости обучения. Вместо этого система использует фиксированные или ключевые веса связей и динамически адаптируемые пороги активации для обеспечения строгой обратимости и детерминированного восстановления состояния, формируя стационарный псевдо-стохастический процесс во время ее работы.

Актуальность разработки обусловлена растущим спросом на энергоэффективные, аппаратно-дружелюбные и потенциально пост-квантовые криптографические примитивы, особенно в условиях развития edge-вычислений и нейроморфных технологий.

Архитектура системы

Система состоит из двух взаимодействующих слоёв:

Двухкомпонентный слой: отвечает за распространение сигнала. Элемент активируется, если сумма входящих сигналов из его окрестности размером n×n (n < M) превышает фиксированный порог (сумма > порог).

Трёхкомпонентный буферизованный слой: обеспечивает стабильность и обратимость. Элемент активируется только при точном равенстве суммы динамически регулируемому порогу (сумма == порог). Пороги адаптируются на каждом шаге, следуя логике работы и сохраняя биективность отображения. Функции срабатывания с использованием порогов могут быть различными.

Криптографический ключ задаётся весами связей (±1) между элементами и их окрестностями 4D-тензором: cb [i,j,k,l], где (i,j) — координаты активируемого элемента, а (k,l) — индексы элементов в его окрестности.

В текущей программной реализации, подтверждающей логику работы модели, обработка элементов на шаге выполняется последовательно — в силу ограничений архитектуры обычного CPU. Однако сама структура алгоритма — полностью параллелизуема: каждый элемент на шаге зависит только от состояния своей локальной окрестности на предыдущем шаге, что позволяет выполнять активацию всех элементов слоя одновременно.

Таким образом, при аппаратной реализации на FPGA или нейроморфных чипах (Intel Loihi, IBM TrueNorth) обработка может быть выполнена параллельно по всему слою за один такт, что обеспечивает константное время выполнения шага O(1), независимое от размера массива. Это — ключевое преимущество предлагаемой архитектуры, открывающее путь к высокоскоростной обработке больших объёмов данных.

Структурная логика (концептуальная визуализация)

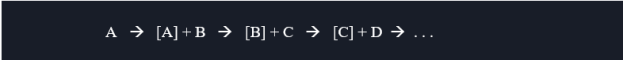

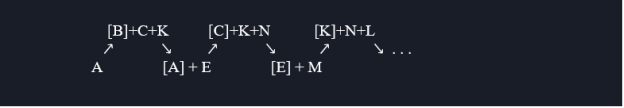

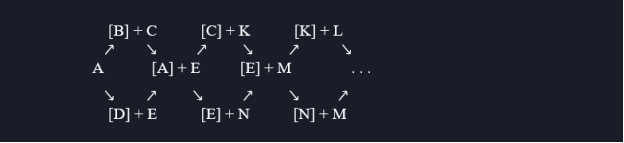

Траектория активации следует симметричному шаблону с переключением между слоями — концептуально это можно представить следующим образом:

Однослойная 2-х компонентная сеть:

Двухслойная 2-х и 3-х компонентная сеть:

Трёхслойная 2-х компонентная сеть:

Здесь наборы из активных элементов в квадратных скобках [] обозначают состояние предыдущего шага, а наборы без скобок — текущего шага. Симметричная активация как слева (прямой ход), так и справа(обратный ход) обеспечивает точное восстановление исходного состояния при обратном проходе того же алгоритма, что и при прямом.

Для предотвращения возможного зацикливания состояний архитектура поддерживает многослойные конфигурации — каждый слой может иметь независимо сгенерированную случайную топологию связей. В текущей реализации используется структура из двух- и трёхкомпонентных слоёв для обеспечения стабильности. Зацикливание одного блока (повторение состояний) на каком-то шаге шифрации не ведет к невозможности шифрации.

Трехслойная модель, при использовании для шифрации крайних слоев, допускает произвольное расщепление шифротекста при шифрации и дешифрации, что приводит к различным траекториям активации, но всегда — к одному и тому же исходному состоянию. Это свойство не является криптографическим примитивом, но может использоваться для затруднения анализа траекторий злоумышленником, а также как иллюстрация принципа «дегенерации» — свойства, характерного для живых и сложных систем.

Блочное шифрование и аппаратная реализация

Система реализует блочное шифрование, где блок данных равен размеру массива N×N. Процесс шифрования состоит из фиксированного числа итераций (для шифрации достаточно одной), после чего массив передаётся в зашифрованном виде. Дешифрование осуществляется по тому же алгоритму в обратном порядке — с тем же ключом и с гарантией восстановления исходного состояния.

Хотя текущая программная реализация выполняется последовательно, архитектура изначально спроектирована для параллельного исполнения на специализированном оборудовании, что позволяет прогнозировать значительный прирост производительности при реализации на FPGA или нейроморфных платформах.

В предлагаемой модели не требуется памяти для хранения истории или таблиц подстановок — только текущее и предыдущее состояния активации. Это делает систему идеальной для встраивания в аппаратные модули безопасности, IoT-устройства и edge-системы.

Экспериментальная верификация

Система протестирована на массивах:

7×7: входной паттерн → 1..10^5 шага вперёд → хаос → 1..10^5 шага назад → точное восстановление.

77×77: подтверждена стабильность, отсутствие сбоев и потерь обратимости.

Все операции на шаге в текущей реализации — последовательны. Скорость работы на нейроморфных структурах предстоит измерить в будущих исследованиях.

Большое количество итераций 10^5 и более в исследовании использовалось для подтверждения логики обратимости системы. Системы может уходить в зацикленность на определенном шаге, особенно при малых размерностях массива N*N<(15*15), но обратимость всегда сохраняется.

Система обладает высокой чувствительностью к изменению входных данных: потеря даже одного бита делает восстановление невозможным, что обеспечивает защиту от частичного перехвата, но требует надёжного канала передачи. Пространство ключей формируется комбинацией: (1) тензора связей (±1 веса), (2) начальных порогов элементов, (3) последовательности режимов активации (их может быть один или несколько), (4) количества шагов — что в целом даёт экспоненциально большое пространство ключей. Для предотвращения зацикливания (теоретически возможного, но маловероятного при больших размерах массива) система допускает адаптацю количества шагов.

Обсуждение и перспективы

Архитектура открывает новые направления:

Пост-квантовая криптография: сложность восстановления ключа без знания траектории.

Энергоэффективные вычисления: строгая обратимость → потенциально нулевое тепловыделение (по Ландауэру).

Нейроморфная безопасность: интеграция криптографии прямо в «нейронную» архитектуру чипа.

Дальнейшие исследования могут быть направлены на:

– Формализацию доказательства обратимости.

– Оптимизацию под конкретные аппаратные платформы.

– Сравнение скорости и безопасности с AES/ChaCha20 на FPGA/Loihi.

– Измерение реальной производительности на нейроморфных чипах.

Заключение

Предложенная архитектура представляет собой новый класс строго обратимых криптографических примитивов, сочетающий в себе идеи нейронных сетей, пороговой логики и блочного шифрования. Её ключевые потенциальные преимущества — параллельность, аппаратная эффективность, масштабируемость и строгая обратимость — делают её перспективной для внедрения в современные системы защиты данных, особенно в условиях развития нейроморфных и энергоэффективных вычислений. Текущая программная реализация подтверждает корректность и обратимость системы; следующим шагом является её аппаратная реализация и измерение производительности.

Литература:

- Toffoli T. Reversible Computing // Automata, Languages and Programming. — 1980.

- Intel Labs. Loihi 2: A Neuromorphic Research Chip. — 2021.

- Яндекс. Облачные технологии и безопасность. — https://yandex.ru

- ГОСТ Р 50922–2008. Защита информации. Основные термины и определения.